張凱鈞

得獎論文題目: 基於圖神經網路之通用的時序模型萃取方法

本校學士班學生論文獎獎勵對象限本校學士班在學學生且為論文之主要研究者及撰稿者,論文之研究工作主體必須在本校就學期間完成。獎項分為學士班學生論文傅斯年獎、校長獎、院長獎及優良獎四類。2022年榮獲本校傅斯年獎的學生僅有5名。

↑張凱鈞同學發表論文。

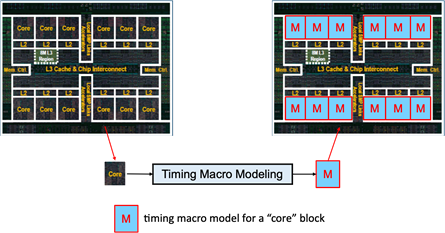

↑時序模型萃取 (timing macro modeling) 示意圖。

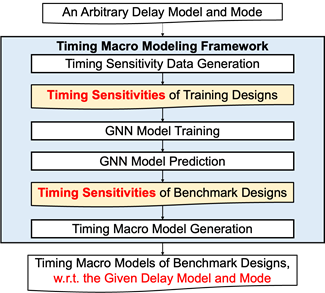

↑本研究提出之演算法。

時序分析 (static timing analysis) 是IC設計流程中相當重要的步驟,然而其運算複雜度相當高。因此,隨著IC設計複雜度持續提升,時序分析已成為IC設計流程中的瓶頸。為了提升時序分析的效率,階層式 (hierarchical) 及平行化 (parallel) 的時序分析開始被廣泛採用,而時序模型萃取 (timing macro modeling) 正是其中的關鍵。

一個好的萃取式時序模型,必須要精準地留下對時序影響大的電路元件接腳 (pin),並移除影響輕微的接腳,才能有效壓縮模型大小以提升時序分析效率,並同時兼顧時序分析的準確性。過去的研究中,往往仰賴非一般化的方法 (heuristics) ,或是使用者需要花費大量時間調整參數,在時序模型表現上及通用性上均有改善空間。

本研究中,我們觀察到圖神經網路 (graph neural networks, GNN) 有很多特性適合運用在時序模型萃取中。因此,我們提出了一個基於圖神經網路的演算法。首先,我們設計了一個量度標準來評估每個接腳對整體時序分析準確度造成的影響,並以此產生訓練資料 (training data);接著,搭配電路的架構 (topology),讓圖神經網路來學習、並藉此辨認出測試資料 (testing data) 中高影響力的接腳。實驗結果顯示,透果我們的演算法產生的萃取式時序模型可以達成與最新研究 (state-of-the-art) 相近的時序分析準確性,同時還能縮小10%的模型大小。實驗也證明我們的演算法可以套用到不同的時序分析模式上。

未來研究中,我們計畫將我們的方法延伸到多重邊界案例 (multi-corner) 與多重操作模式 (multi-mode) 之時序分析上,這也是業界亟需的應用。

最後,要特別感謝江蕙如教授的指導,以及李培瑜博士、姜鈞堯學長的合作與貢獻。也要感謝學士班學生論文獎評審委員們對本研究的肯定。本研究初步成果已發表於電子設計自動化領域頂級會議 2022 Design Automation Conference (DAC) 上,題目為 Timing Macro Modeling with Graph Neural Networks。

張凱鈞,電機系大學部2022年畢業生,現於電子所擔任研究助理。