由本系劉致為教授及其研究團隊的Beyond 2nm技術節點研究成果,於2021年6月在半導體領域的國際頂尖會議VLSI 2021發表,並獲選為highlight paper,且於7月底獲國際頂尖期刊Nature Electronics Research Highlight報導。此外也於2021年12月在國際頂尖會議IEDM 2021發表,並入選最佳學生論文獎。

隨著科技日新月異,半導體晶片與人類的生活密不可分,先進半導體晶片的需求急遽增長,效能也不斷提升,臺灣的半導體產業在全世界有舉足輕重的地位。台積電於5奈米技術節點量產擁有高遷移率通道(high mobility channel)之元件,使用高遷移率通道,猶如駕駛跑車,速度更快,使電晶體的效能更佳。台積電也宣布將於2奈米技術節點採用三層通道之Gate-All-Around(GAA)電晶體結構,使用GAA電晶體結構,猶如使用強力水龍頭,滴水不漏,使電晶體有效降低漏電流,更加節能省電。並搭配通道堆疊(channel stacking)技術,猶如建構雙層高架橋,在相同佔地面積下,可負載更多車流量,使電晶體擁有更高電流且增加電晶體密度,有效提升元件效能。因此高遷移率高層數堆疊通道之GAA電晶體,為beyond 2nm技術節點的發展趨勢。

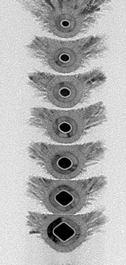

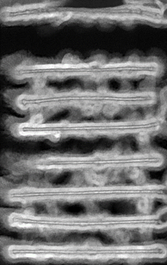

劉教授研究團隊在國際頂尖會議VLSI 2021,發表世界首顆七層堆疊鍺矽通道N型電晶體(7 stacked Ge0.95Si0.05 nanowires)(圖一),與國際標竿相比,其電流為鍺/鍺矽三維電晶體之世界紀錄,此成果也獲國際頂尖期刊Nature Electronics Research Highlight報導。劉教授研究團隊也在國際頂尖會議IEDM 2021,發表世界首顆八層堆疊鍺錫極薄通道P型電晶體(8 stacked Ge0.9Sn0.1 ultrathin bodies)(圖二),利用極薄的3nm通道厚度,有效降低漏電流,其開關電流比為鍺/鍺錫三維電晶體之世界紀錄,此論文也入選IEDM最佳學生論文獎。由此可見高層數通道堆疊與極薄通道之GAA電晶體為未來技術節點之一大趨勢。目前臺大乃是業界以外,唯一能研發出多層通道堆疊之GAA電晶體的大學。劉教授研究團隊持續研究更高層數通道堆疊、更薄通道厚度之GAA 電晶體,以擁有更高的電流及開關電流比,才能使半導體晶片效能更高、更省電,進而使科技持續進步,為人類帶來更好的生活。

圖一、七層堆疊鍺矽通道N型電晶體

圖二、八層堆疊鍺錫極薄通道P型電晶體